# **Machine-Level Programming I: Basics**

CSci 2021: Machine Architecture and Organization Lectures #7-8, February 4th-6th, 2015

Your instructor: Stephen McCamant

#### Based on slides originally by:

Randy Bryant, Dave O'Hallaron, Antonia Zhai

# **Today: Machine Programming I: Basics**

- History of Intel processors and architectures

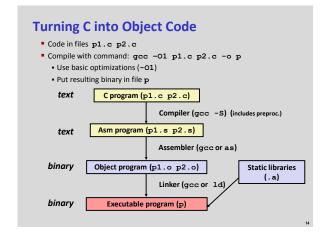

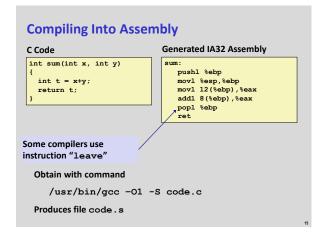

- C, assembly, machine code

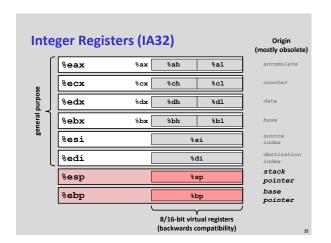

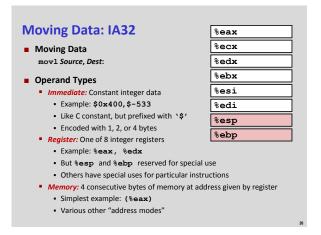

- Assembly Basics: Registers, operands, move

- Intro to x86-64

#### **Intel x86 Processors**

- Dominant in laptop/desktop/server market

- Second place: compatible designs from AMD

- **■** Evolutionary design

- Backwards compatible through 8086, introduced in 1978

- Added more features as time goes on

- Complex instruction set computer (CISC)

- Many different instructions with many different formats

- But, only a subset encountered with Linux/GCC programs

- Alternative Reduced Instruction Set Computer (RISC) designs have theoretical advantages

- Intel borrows ideas from RISC while keeping CISC compatibility

- RISC-style ARM dominates lower-power (e.g. phone) market

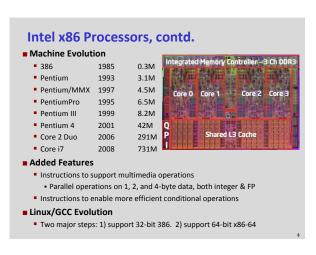

### Intel x86 Evolution: Milestones

Our xA-B machines are a similar-vintage "Xeon"

| Name                            | Date            | Transistors              | MHz            |

|---------------------------------|-----------------|--------------------------|----------------|

| <b>8086</b>                     | 1978            | 29K                      | 5-10           |

| First 16-bit                    | orocessor. Ba   | sis for IBM PC & DOS     |                |

| <ul><li>1MB segme</li></ul>     | nted address    | space (640KB program I   | imit)          |

| <b>(80)386</b>                  | 1985            | 275K                     | 16-33          |

| First 32 bit p                  | rocessor , ref  | erred to as IA32         |                |

| <ul> <li>Added "flat</li> </ul> | addressing"     |                          |                |

| Capable of r                    | unning Unix v   | vith virtual memory      |                |

| ■ 32-bit Linux                  | /gcc uses no ii | nstructions introduced i | n later models |

| ■ Pentium 4F                    | 2004            | 125M                     | 2800-3800      |

| First 64-bit                    | processor, refe | erred to as x86-64       |                |

| Core i7                         | 2008            | 731M                     | 2667-3333      |

#### **Intel x86 Processors: Overview** Architectures **Processors** X86-16 8086 286 X86-32/IA32 486 Pentium Pentium MMX Pentium Pro SSF Pentium III Pentium 4 SSE2 Pentium 4 "E" X86-64 / EM64t **AMD Opteron** Core 2 Duo Core i7 IA: often redefined as latest Intel architecture

# New Species: IA64 aka IPF aka Itanium,...

Date 2001 **Transistors**

■ Itanium

25M + cache?

- First shot at 64-bit architecture: first called IA64

- Radically new instruction set designed for high performance

- Can run existing IA32 programs

- On-board "x86 engine"

- Joint project with Hewlett-Packard

■ Itanium 2

2002

221M

- Big performance boost

- Itanium 2 Dual-Core 2006 1.7B

- Itanium has not taken off in marketplace

- Lack of backward compatibility, no good compiler support, Pentium

# x86 Clones: Advanced Micro Devices (AMD)

- Historically

- AMD has followed just behind Intel

- A little bit slower, a lot cheaper

- Recruited top circuit designers from Digital Equipment Corp. and other downward trending companies

- Built Opteron: tough competitor to Pentium 4

- Developed x86-64, their own extension to 64 bits

#### Intel's 64-Bit

- Intel Attempted Radical Shift from IA32 to IA64

- Totally different architecture (Itanium)

- Executes IA32 code only as legacy

- Performance disappointing

- AMD Stepped in with Evolutionary Solution

- x86-64 (now also called "AMD64")

- Intel Felt Obligated to Focus on IA64

- Hard to admit mistake or that AMD is better

- 2004: Intel Announces EM64T extension to IA32

- Extended Memory 64-bit Technology (now "Intel 64")

- Almost identical to x86-64!

- All but low-end x86 processors support x86-64

- But, lots of code still runs in 32-bit mode

# **Our Coverage**

- x86-32/IA32

- The traditional x86

- x86-64/EM64T/AMD64/Intel 64/x64

- The emerging standard

- Presentation

- Book presents IA32 in Sections 3.1—3.12

- Covers x86-64 in 3.13

- We will cover both interleaved

- Labs will be mostly based on IA32

# **Today: Machine Programming I: Basics**

- History of Intel processors and architectures

- C, assembly, machine code

- Assembly Basics: Registers, operands, move

- Intro to x86-64

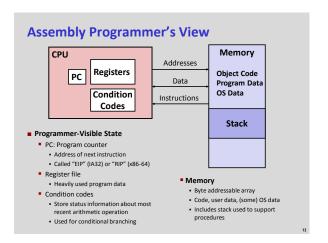

# **Definitions**

- Architecture: (also instruction set architecture: ISA) The parts of a processor design that one needs to understand to write assembly code.

- Examples: instruction set specification, registers.

- Microarchitecture: Implementation of the architecture.

- Examples: cache sizes and core frequency.

- Example ISAs (Intel): x86, Itanium

2

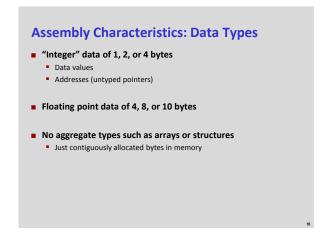

# Assembly Characteristics: Operations Perform arithmetic function on register or memory data Transfer data between memory and register Load data from memory into register Store register data into memory Transfer control Unconditional jumps to/from procedures Conditional branches

#

```

Today: Machine Programming I: Basics

History of Intel processors and architectures

C, assembly, machine code

Assembly Basics: Registers, operands, move

Intro to x86-64

```

```

mov1 Operand Combinations

Source

Dest

Src,Dest

C Analog

movl $0x4,%eax

temp = 0x4;

Reg

lmm

Mem movl $-147, (%eax)

*p = -147;

Reg

temp2 = temp1;

movl %eax, %edx

movl

Reg

Mem

movl %eax,(%edx)

*p = temp;

movl (%eax), %edx

Mem

Reg

temp = *p;

Cannot do memory-memory transfer with a single instruction

```

```

Simple Memory Addressing Modes

Normal (R) Mem[Reg[R]]

Register R specifies memory address

movl (%ecx), %eax

Displacement D(R) Mem[Reg[R]+D]

Register R specifies start of memory region

Constant displacement D specifies offset

movl 8 (%ebp), %edx

```

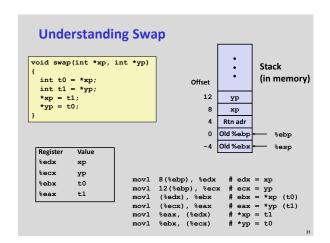

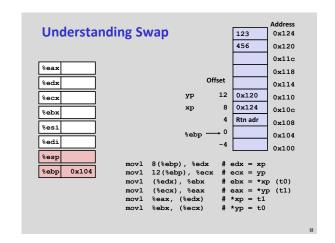

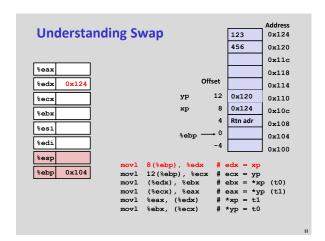

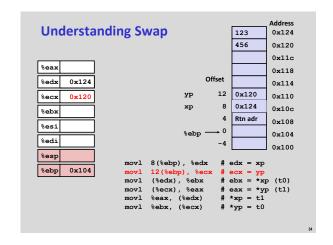

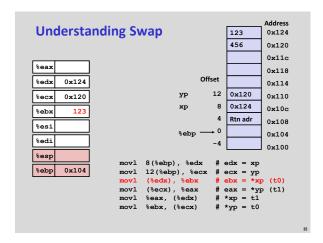

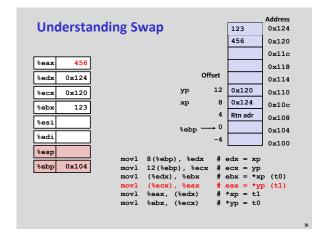

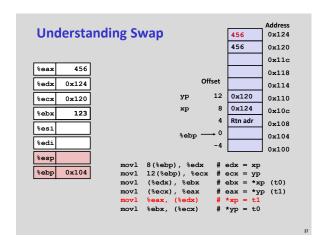

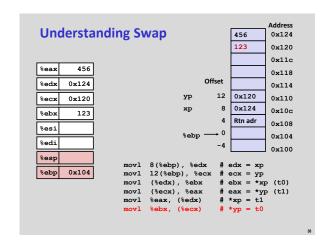

```

Using Simple Addressing Modes

swap:

pushl %ebp

void swap(int *xp, int *yp)

Set

movl %esp,%ebp

Up

pushl %ebx

int t0 = *xp:

int t1 = *yp;

movl

8(%ebp), %edx

*xp = t1;

*yp = t0;

movl

12(%ebp), %ecx

movl

(%edx), %ebx

Body

movl

(%ecx), %eax

%eax, (%edx)

movl

%ebx, (%ecx)

movl

popl

%ebx

%ebp

popl

Finish

ret

```

```

Using Simple Addressing Modes

swap:

pushl %ebp

void swap(int *xp, int *yp)

Set

movl %esp,%ebp

pushl %ebx

Up

int t0 = *xp

int t1 = *yp;

mov1 8(%ebp), %edx

*xp = t1;

*yp = t0;

movl 12(%ebp), %ecx

movl (%edx), %ebx

Body

movl (%ecx), %eax

movl %eax, (%edx)

movl %ebx, (%ecx)

popl

%ebp

Finish

```

# **Complete Memory Addressing Modes** ■ Most General Form D(Rb,Ri,S) Mem[Reg[Rb]+S\*Reg[Ri]+ D] D: Constant "displacement" 1, 2, or 4 bytes ■ Rb: Base register: Any of 8 integer registers Ri: Index register: Any, except for %esp • Unlikely you'd use %ebp, either Scale: 1, 2, 4, or 8 (why these numbers?) ■ Special Cases Mem[Reg[Rb]+Reg[Ri]] (Rb,Ri) D(Rb,Ri) Mem[Reg[Rb]+Reg[Ri]+D] (Rb,Ri,S) Mem[Reg[Rb]+S\*Reg[Ri]]

# Logistics Break: Turning In Lab 1 is due tonight by 11:55pm (A few of you have already submitted it, congrats) Reminder: make sure driver.pl works! Homework assignment 1 is due at the beginning of class (3:35pm) Monday Only option for full credit is turning in on paper at beginning of class Late paper submissions accepted through end of lecture All other late submissions must be online on the Moodle Other homework notes: Only problems 3 and 4 need be submitted for grading A computer printout is strongly recommended/requested

| Sizes of C Objects (in Bytes)   |                |            |        |  |  |

|---------------------------------|----------------|------------|--------|--|--|

| C Data Type                     | Generic 32-bit | Intel IA32 | x86-64 |  |  |

| <ul> <li>unsigned</li> </ul>    | 4              | 4          | 4      |  |  |

| • int                           | 4              | 4          | 4      |  |  |

| <ul> <li>long int</li> </ul>    | 4              | 4          | 8      |  |  |

| • char                          | 1              | 1          | 1      |  |  |

| <ul><li>short</li></ul>         | 2              | 2          | 2      |  |  |

| <ul><li>float</li></ul>         | 4              | 4          | 4      |  |  |

| <ul><li>double</li></ul>        | 8              | 8          | 8      |  |  |

| <ul> <li>long double</li> </ul> | 8              | 10/12      | 16     |  |  |

| • char *                        | 4              | 4          | 8      |  |  |

```

32-bit code for swap

swap:

pushl %ebp

void swap(int *xp, int *yp)

Set

movl %esp,%ebp

Up

int t0 = *xp;

int t1 = *yp;

*xp = t1;

movl

8(%ebp), %edx

*yp = t0;

movl

12(%ebp), %ecx

movl

(%edx), %ebx

Body

(%ecx), %eax

%eax, (%edx)

movl

movl

%ebx, (%ecx)

movl

popl

%ebx

popl

%ebp

Finish

ret

```

```

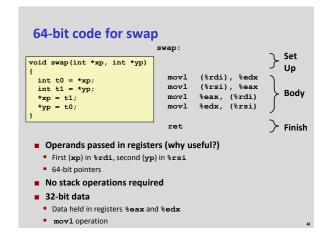

64-bit code for long int swap

swap_1:

} Set

void swap(long *xp, long *yp)

Up

(%rdi), %rdx

long t0 = *xp;

long t1 = *yp;

*xp = t1;

movq

movq

(%rsi), %rax

- Body

movq

%rax, (%rdi)

*yp = t0;

movq

%rdx, (%rsi)

ret

> Finish

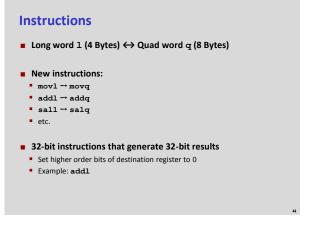

■ 64-bit data

■ Data held in registers %rax and %rdx

movqoperation

• "q" stands for quad-word

```

```

History of Intel processors and architectures

Evolutionary design leads to many quirks and artifacts

C, assembly, machine code

Compiler must transform statements, expressions, procedures into low-level instruction sequences

Assembly Basics: Registers, operands, move

The x86 move instructions cover wide range of data movement forms

Intro to x86-64

A major departure from the style of code seen in IA32

```